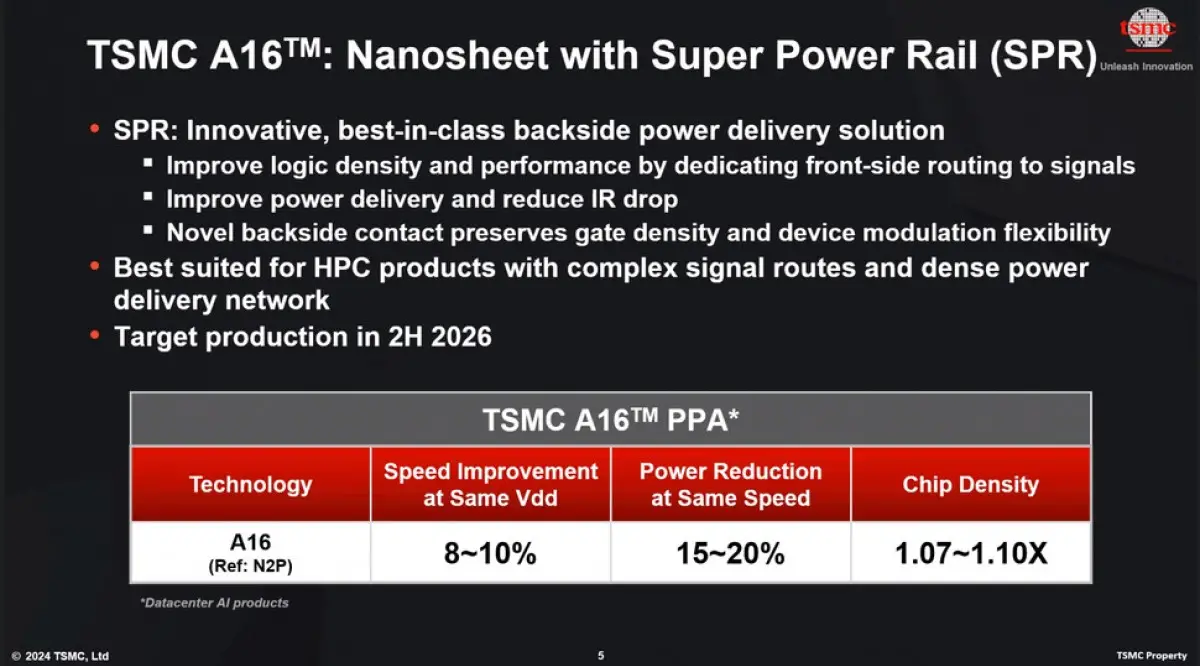

TSMC Kenalkan Teknologi Proses 1,6 nm, Lebih Efisien dan Berperforma Tinggi

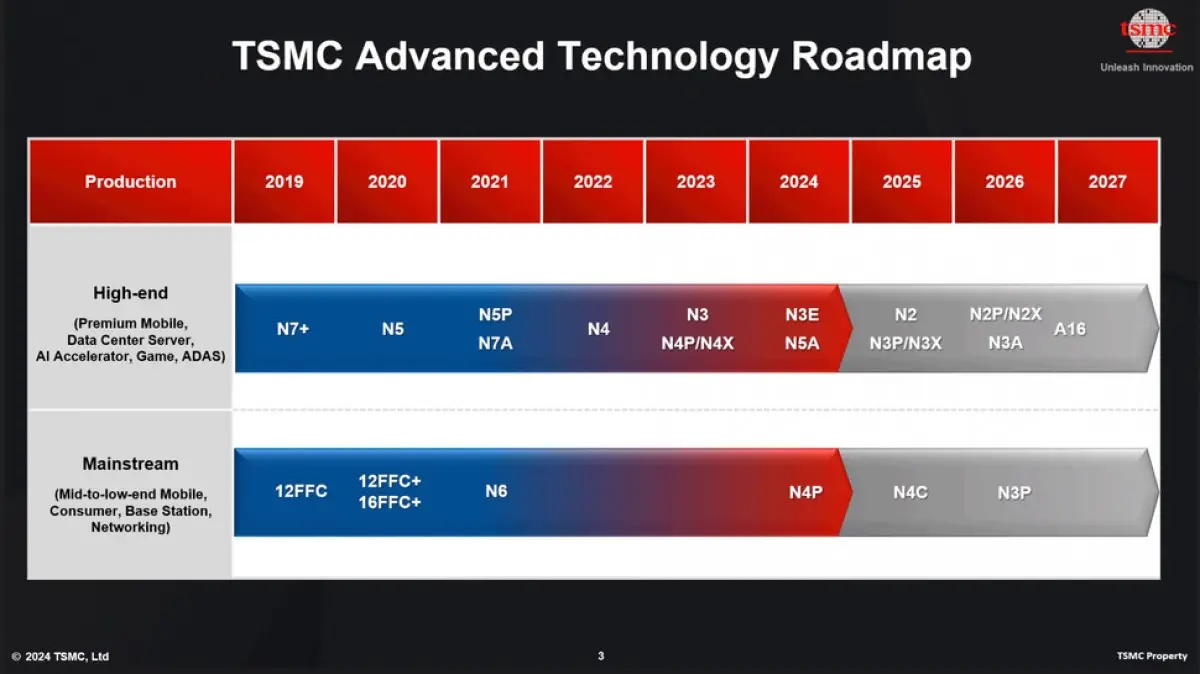

TSMC telah mengumumkan teknologi proses manufaktur 1,6nm untuk chip yang sekaligus mencakup jaringan pengiriman daya bagian belakang yang lebih meningkatkan efisiensi daya dan kepadatan transistor.

Melansir GSM Arena, proses 1,6nm ini akan bergantung kepada transistor nanosheet gate-all-around seperti arsitektur N2, N2P, dan N2X yang akan datang dengan berdasarkan node 2nm. Proses manufaktur chip baru ini akan memungkinkan peningkatan yang signifikan, seperti kecepatan clock 10% lebih tinggi pada voltase yang sama, serta pengurangan pengurasan daya hingga 20% lebih rendah di frekuensi dan kompleksitas yang sama. Bahkan, tergantung dari desain chipnya, proses ini juga bisa memuat transistor 10% elbih banyak.

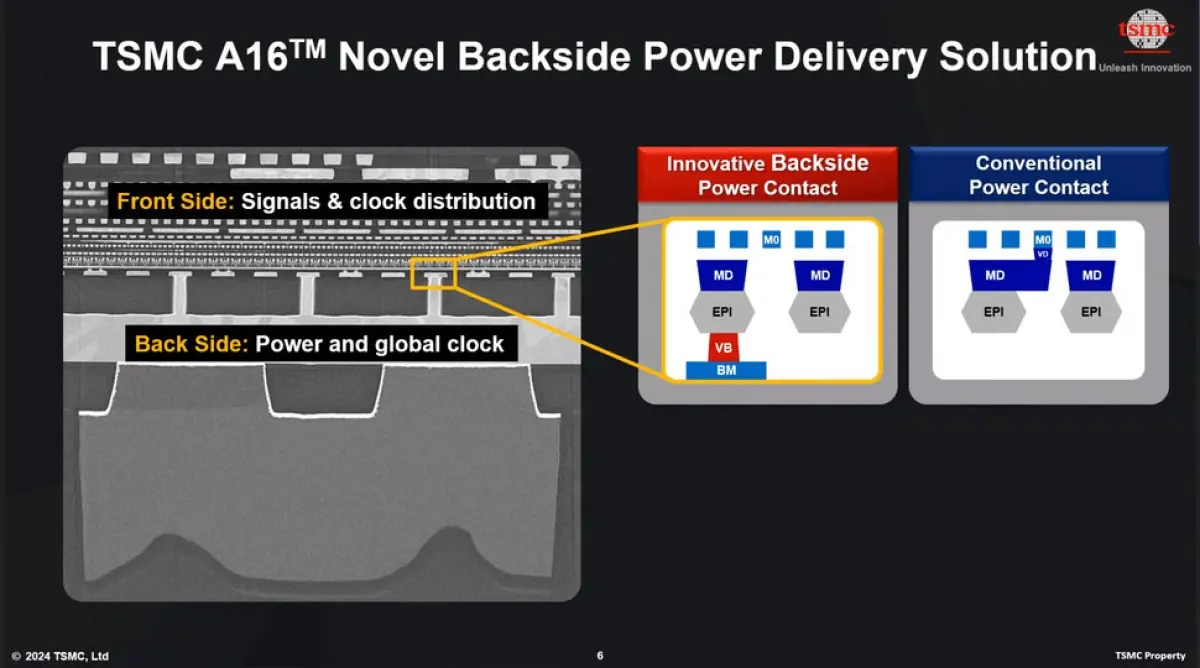

Jaringan pengiriman daya bagian belakang (backside power delivery network) juga dijamin akan lebih bertenaga di chip masa depan ini karena kepadatan transistor dan pengiriman daya yang ditingkatkan, dan secara keseluruhan akan mempengaruhi performanya. TSMC juga menyebutkan bahwa jaringan pengiriman daya belakang ini akan mampu meningkat berkat prosesor AI dan HPC yang memerlukan kabel sinyal lebih kompleks dan jaringan listrik yang padat.

Pihak TSMC menyebutkan bahwa jadwal produksi untuk proses 1,6nm ini akan dijadwalkan pada paruh kedua tahun 2026 mendatang, dan jika lancar, pengiriman produk akan siap pada tahun 2027.

(sumber)